第1页 / 共14页

试读已结束,还剩13页,您可下载完整版后进行离线阅读

THE END

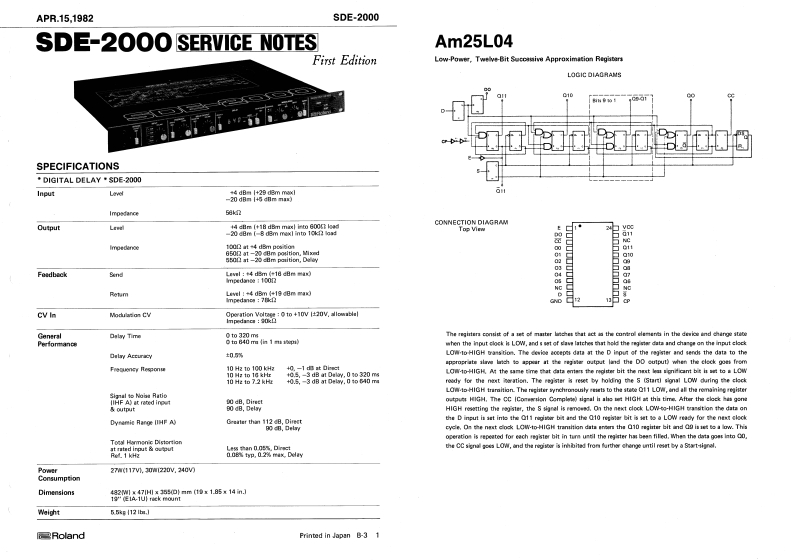

APR.15,1982SDE-2000SDE-2000 SERVICE NOTESAm25L04First EditionLow-Power.Twelve-Bit Approximation RegibarsLOGIC DIAORANS10SPECIFICATIONS·DIGITAL DELAY·sDE-2000InputLImpedance58k12OutputLevdl44 cBm [+18 dsm maxl into 6000 lgedCONNECTION DIAGRAM-20e8m【-8d8 m mexl into1ghas时Top ViewImpedanoeFoedbeckSindLavel t4 d5m (+18 dBm max)pedanoe 10012RetumLavel +4 dBm +19 dBm max)pedanee 7lkCV InModulation CVOperation Voltage to +10v V,allomablelmd"c■:0民山GeneralDalwy Timehe regirtara condtt of a set of martar lnches that act n th由ntrol clemen的in the de地nd chan球ePerforan闭8830a1mhen the input clck is LOW,and s set of dave latches that hold the register data and change on the input clckDalwy Acturacy±0%LOW-Io HIGH.The dewioe aocepes data at the D input of the register and sends the data to theppropriate alrve的a好oar at the regster output land the D0 Culpu0 hen the clock9t时fremFrecueney Responu10H21o100k42104:11gkt8-3dBa10,010320mOW-10-HIG代the sam me that data emars the regitter bit the nest lat口mbsmoLCw10H21e72Hu0.5,-3dB10e.0o40maroody for the net iration.The eegister is reset by holding the S (Startl signal LoW during the clockLOW-D-HIGH traraition.The reghiter synchronouily eeiets to the stabe Q11 LOW,nd all the remaining registernals的6 e Ratio00 dB,Direetoutpuet HIGM.The CC IComersion Complaa)aigeal in ahs t HIGH at thh time.After the clock has goneoutputBO dB.DelayHIGH resetting the register,the S signal is remoend.On the next clock LOW-co-HIGH trandtion the data anDynamig Range IIHF A)the D input is ast into the Q11 regisr bit ard the Q10 regber bit is set a LOW ready for the next clockcycle,Dn the nast clock LOW-to-HIGH tranthtion data anten the 10 megirter bit and o is iet to a low.Thisoge0on移pato同for each时ister bit in tumn until the regirter h国6 en filled,hes the data9 oet intn0Toral Harmonic Dstertiant ratad input&o.中uLess than 0.05%.Directthe CC signal goes LOW,and the regisor is inhibited from further chenge until resat by o Btart-signal.Ret 1 kHz008tP,02%m4关DiyPower27w0117V1.10W22.240V0ConsumptionDimensionsWeight65*81121RolandPrinted in Japan B-3 1

请登录后查看评论内容