第1页 / 共3页

第2页 / 共3页

试读已结束,还剩1页,您可下载完整版后进行离线阅读

THE END

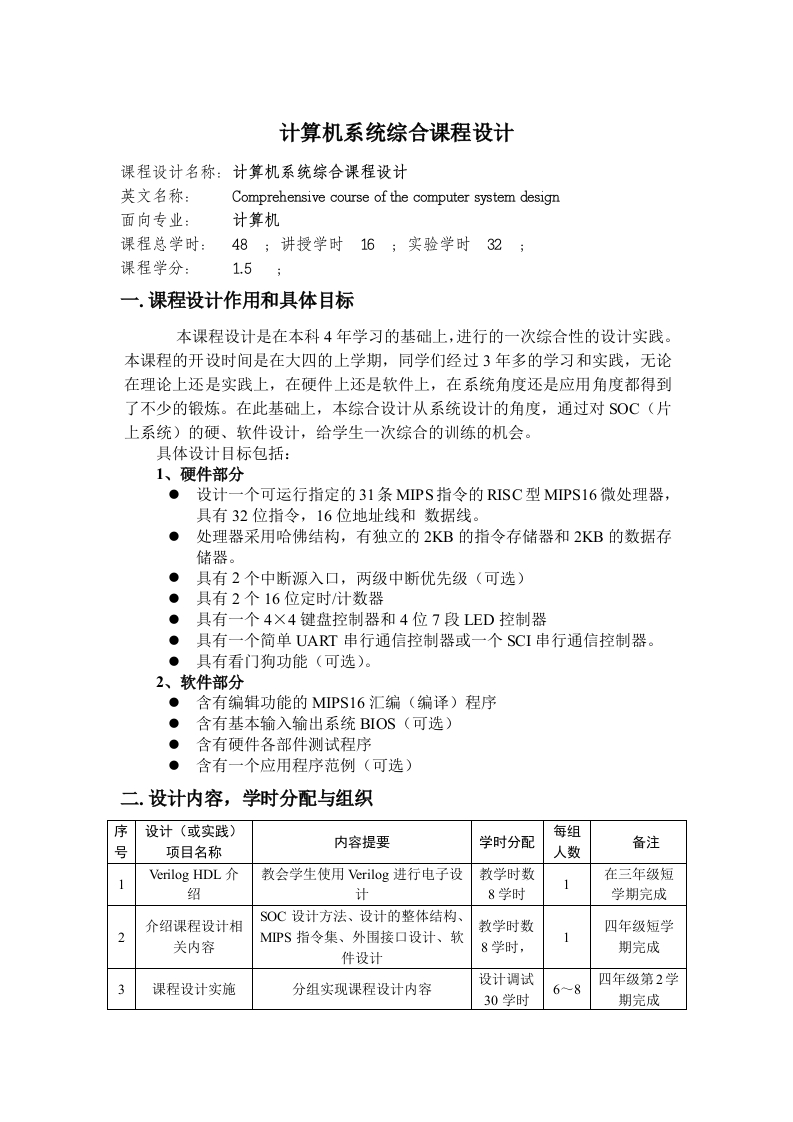

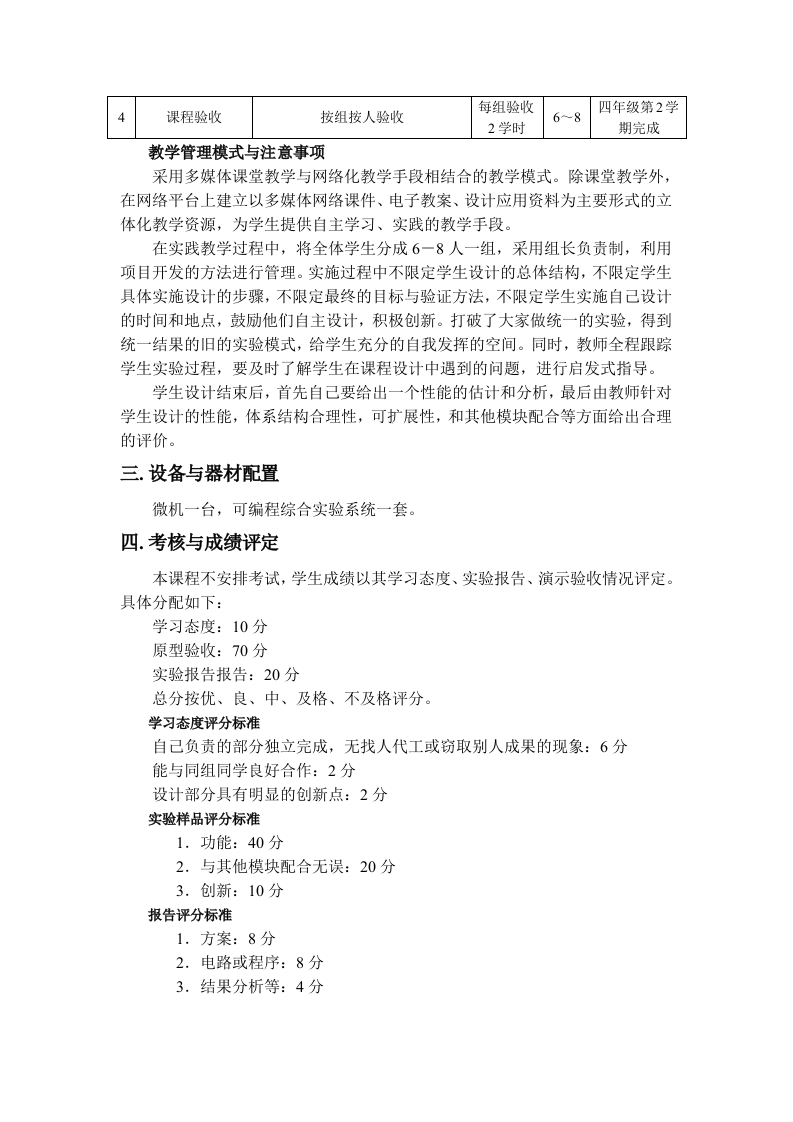

计算机系统综合课程设计课程设计名称:计算机系统综合课程设计英文名称:Comprehensive course of the computer system design面向专业:计算机课程总学时:48;讲授学时16;实验学时32;课程学分:1.5一.课程设计作用和具体目标本课程设计是在本科4年学习的基础上,进行的一次综合性的设计实践。本课程的开设时间是在大四的上学期,同学们经过3年多的学习和实践,无论在理论上还是实践上,在硬件上还是软件上,在系统角度还是应用角度都得到了不少的锻炼。在此基础上,本综合设计从系统设计的角度,通过对SOC(片上系统)的硬、软件设计,给学生一次综合的训练的机会。具体设计目标包括:1、硬件部分●设计一个可运行指定的31条MIPS指令的RISC型MPS16微处理器,具有32位指令,16位地址线和数据线。●处理器采用哈佛结构,有独立的2KB的指令存储器和2KB的数据存储器。·具有2个中断源入口,两级中断优先级(可选)●具有2个16位定时计数器●具有一个4×4键盘控制器和4位7段LED控制器·具有一个简单UART串行通信控制器或一个SCI串行通信控制器。·具有看门狗功能(可选)。2、软件部分·含有编辑功能的MPS16汇编(编译)程序●含有基本输入输出系统BIOS(可选)·含有硬件各部件测试程序·含有一个应用程序范例(可选)二.设计内容,学时分配与组织序设计(或实践)每组号内容提要项目名称学时分配人数备注Verilog HDL介教会学生使用erilog进行电子设教学时数在三年级短1绍计8学时学期完成SOC设计方法、设计的整体结构、介绍课程设计相教学时数四年级短学、2关内容MPS指令集、外围接口设计、软8学时,期完成件设计设计调试四年级第2学3课程设计实施分组实现课程设计内容6-830学时期完成

请登录后查看评论内容