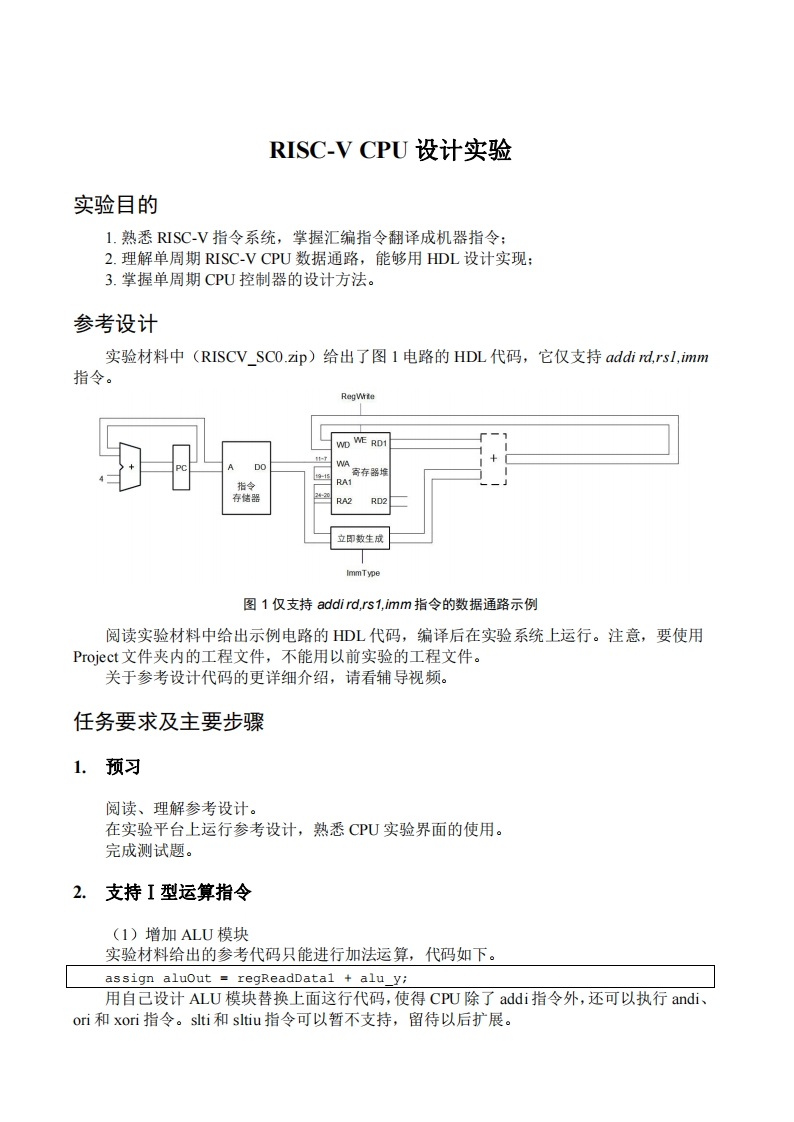

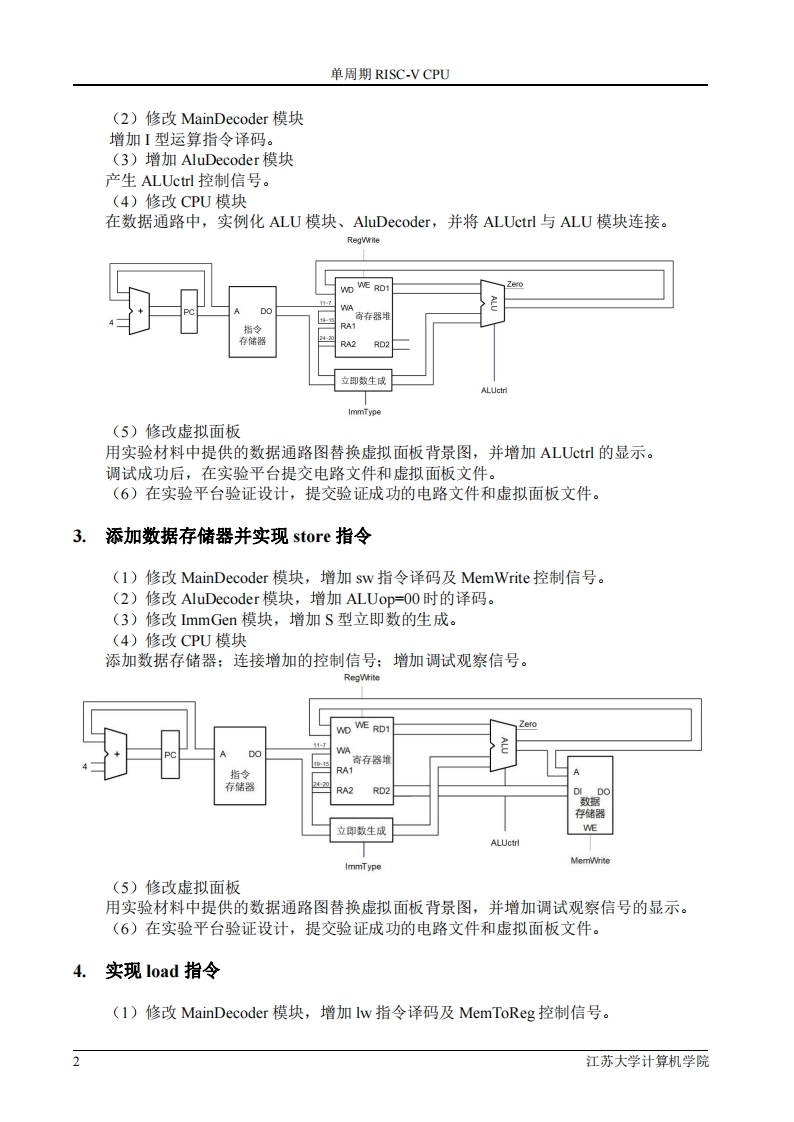

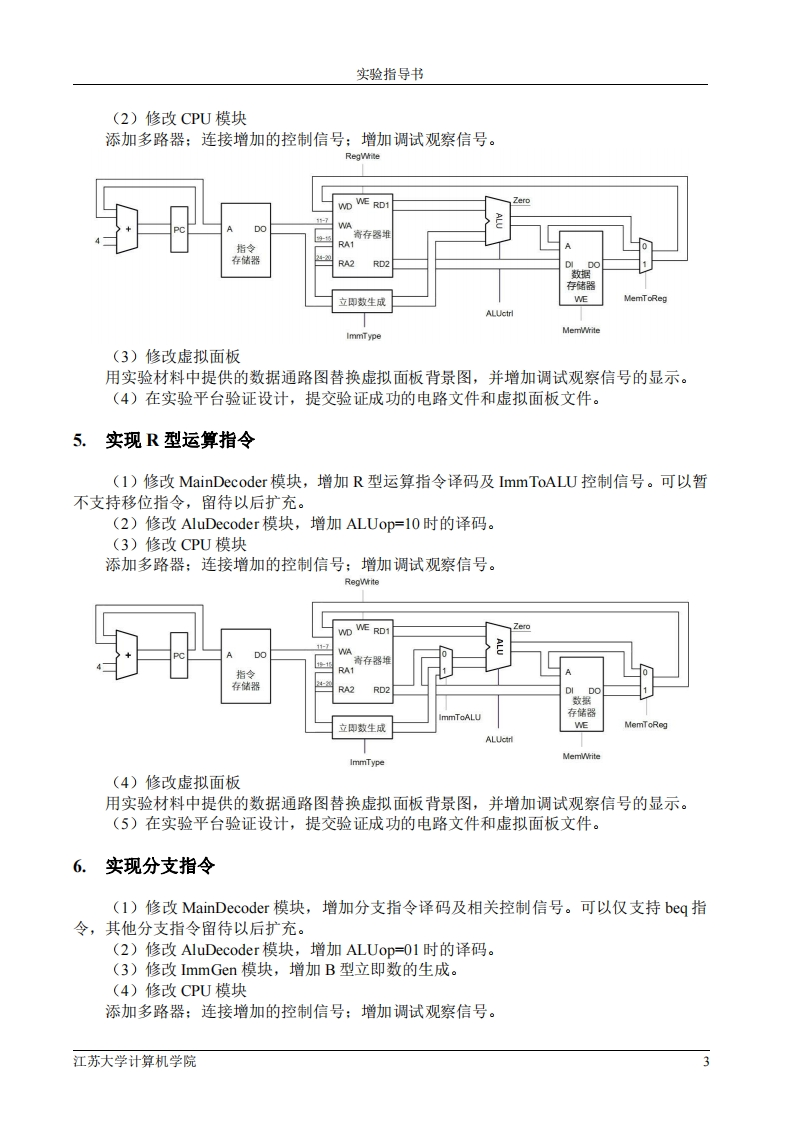

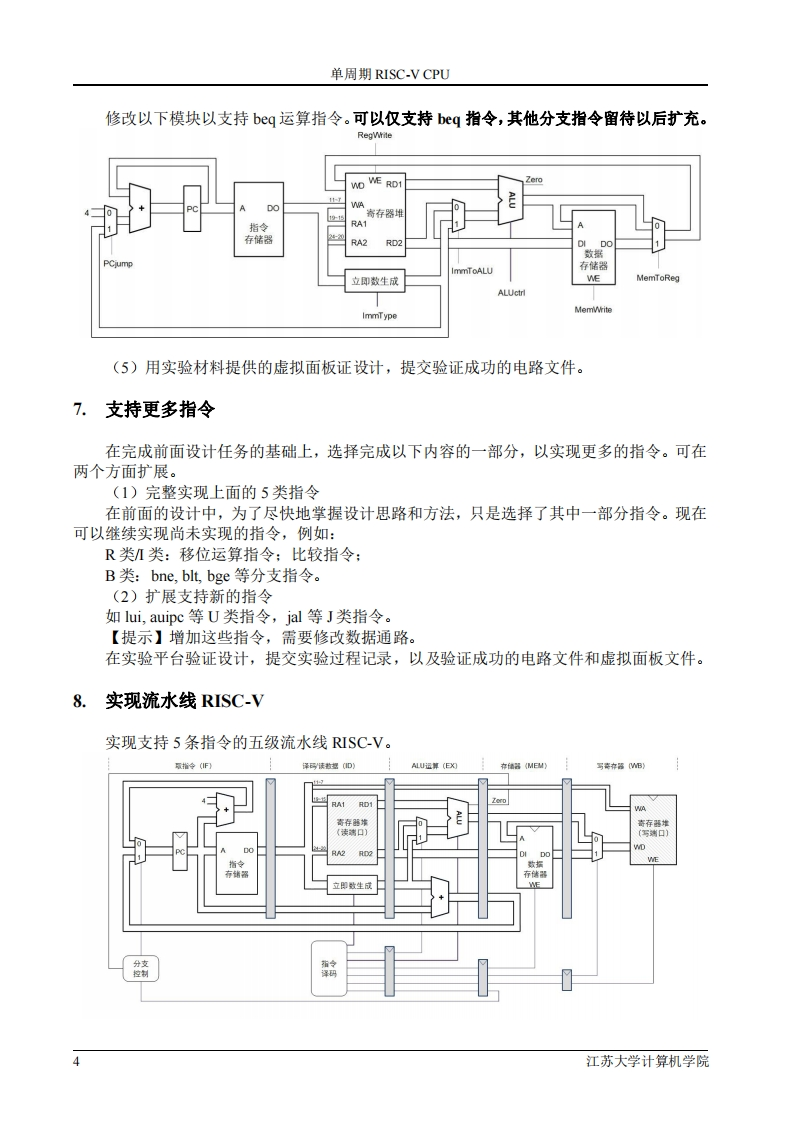

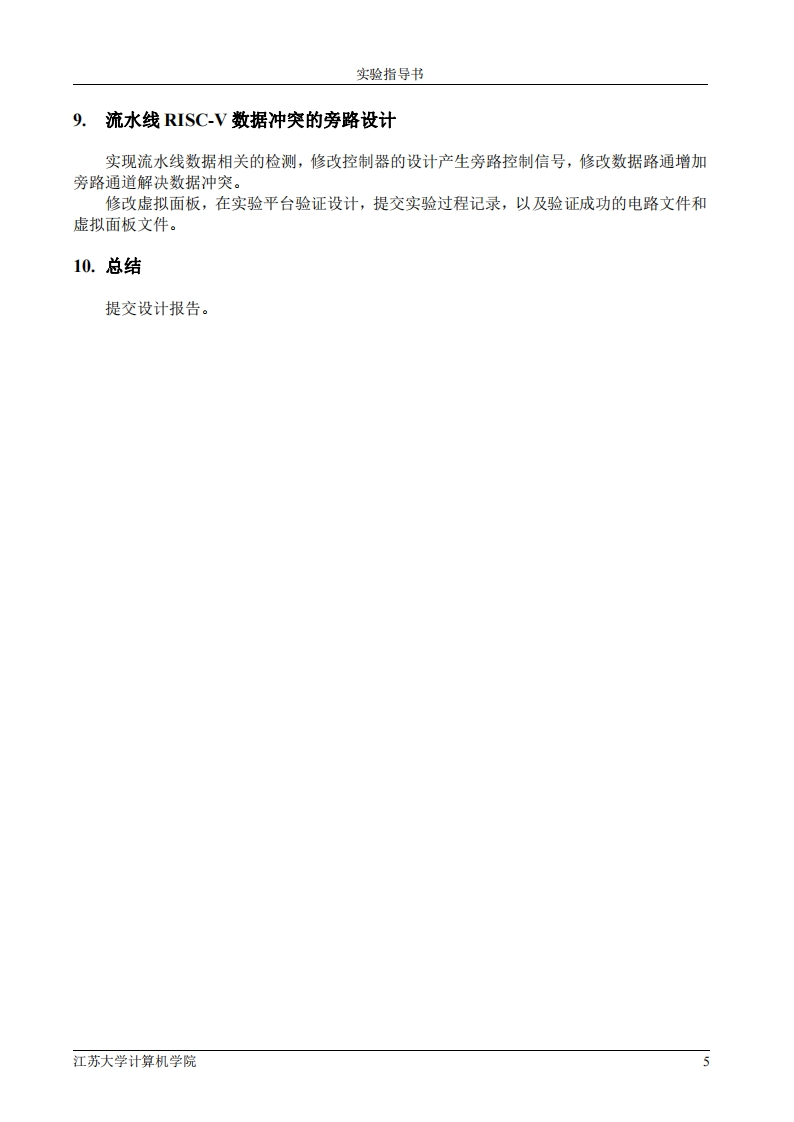

RISC-VCPU设计实验实验目的1.熟悉RISC-V指令系统,掌握汇编指令翻译成机器指令:2.理解单周期RISC-VCPU数据通路,能够用HDL设计实现:3.掌握单周期CPU控制器的设计方法。参考设计实验材料中(RISCV_SC0.zip)给出了图1电路的HDL代码,它仅支持addi ro,rs,imm指令。RegWrteWD WE RD11I-TWA寄存器指令RA1存储器4-3RA2RD2立即数生成图1仅支持addird,rs1,imm指令的数据通路示例阅读实验材料中给出示例电路的HDL代码,编译后在实验系统上运行。注意,要使用Project文件夹内的工程文件,不能用以前实验的工程文件。关于参考设计代码的更详细介绍,请看辅导视频。任务要求及主要步骤1.预习阅读、理解参考设计。在实验平台上运行参考设计,熟悉CPU实验界面的使用。完成测试题。2.支持I型运算指令(1)增加ALU模块实验材料给出的参考代码只能进行加法运算,代码如下。assign aluOut regReadDatal alu_y;用自己设计ALU模块替换上面这行代码,使得CPU除了addi指令外,还可以执行andi、ori和xori指令。slti和sltiu指令可以暂不支持,留待以后扩展。

请登录后查看评论内容